近年来,随着人工智能应用场景的爆发,人工智能算法对算力的需求增长已经显著超越了芯片摩尔定律。传统的计算芯片在计算资源、时延、功耗上越来越无法满足人工智能高并行计算的需要。在智能芯片上,传统的冯诺伊曼架构围绕计算为中心,处理器与存储器本质上是分离的,两者之间的大规模数据搬移进一步制约了人工智能芯片的性能。因此,传统芯片架构面临着“存储墙”、“功耗墙”和“算力墙”等诸多挑战,难以满足人工智能应用的低时延、高能效、高可扩展性的需求。针对上述问题,复旦大学芯片与系统前沿技术研究院刘明院士团队提出了多芯粒的存算一体集成芯片——COMB-MCM(Computing-on-memory boundary – Multi-Chiplet-Module)。

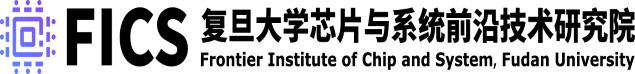

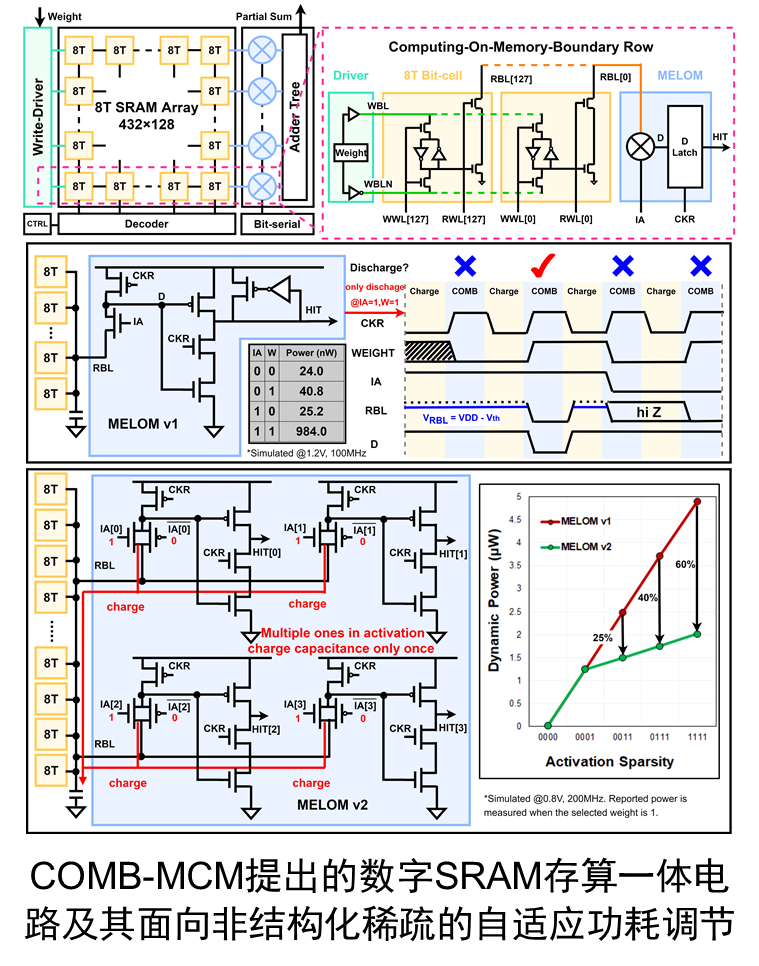

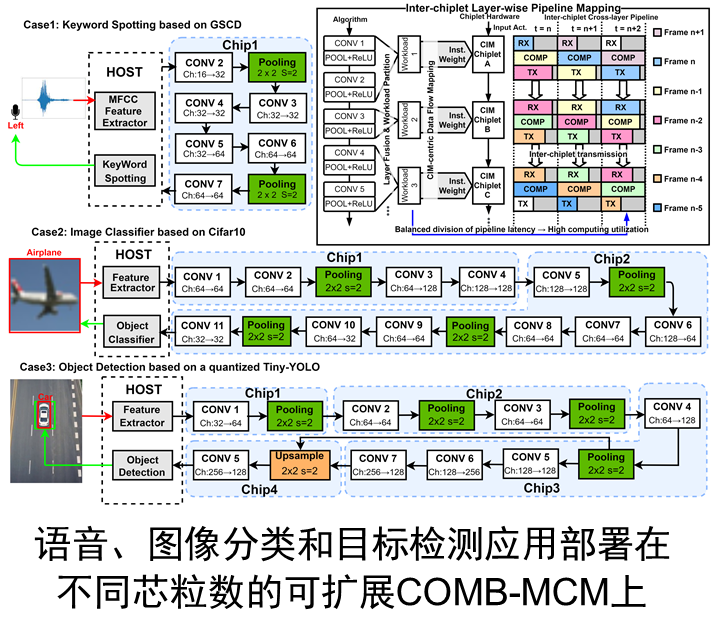

电路上,COMB-MCM采用存算一体设计,通过将数据存储单元和并行计算单元合为一体,以大幅减少片内、片间的数据通信和搬移,达到降低功耗、提高系统算力。与已有基于模拟计算电路的存算一体相比,该工作提出了自适应功耗调节的数字存算一体电路,具有精度无损且支持非结构化稀疏的自适应能效调节特点。架构与系统上,为了适应不同场景和算力需求,COMB-MCM提出了算力可扩展的集成芯片架构,即每个芯粒具有单位计算与存储资源,面对不同规模神经网络时,通过配置芯粒的数量,实现计算与存储需求的按比例增长,可避免了“一系统一设计”的重复研发成本,也为未来单一封装内的异质异构集成提供了一个新的设计思路。实现上,COMB-MCM在65 nm/28nm下分别流片,达到了14TOPS/W和43TOPS/W的计算能效,其中65nm设计基于集成扇出封装 实现了2.5D集成。

相关研究成果以《COMB-MCM: Computing-on-Memory-Boundary NNProcessor with Bipolar Bit-wise Sparsity Optimization for Scalable Multi-Chiplet-Module Edge Machine Learning》被集成电路设计领域奥林比克旗舰会议——国际学术会议ISSCC 2022录用。该论文通讯作者为芯片院青年副研究员陈迟晓,博士生朱浩哲、硕士生焦博、张锦山同学为共同第一作者。